고정 헤더 영역

상세 컨텐츠

본문

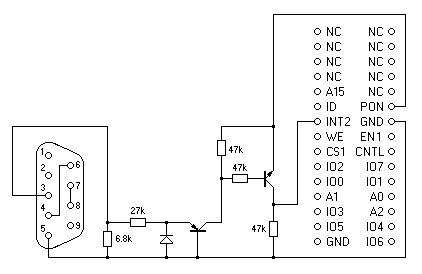

The serial interfaceNext: Up: Previous:The programming of the Helix128-2's internal registers is achieved via a simple serial interface of three lines.In Helix128-2.0/2.1 the three signals involved are SerClk, SerData, and SerLoad, in Helix128-2.2/2.3 SerClk has been merged with Rclk and SerDatawith TrigIn. Thus, in the latter case, programming ofthe registers will give rise to multiple triggers; it is thereforerecommended to keep notReset low during programming.The following explanation applies to Helix128-2.0/2.1, but is easily extended to the new scheme by making the above stated substitution.During programming of the chip Rclk and SerClk must run continously.

Serial Peripheral Interface Protocol

A 20 bit word is applied according to the Helix128-2 data frame (fig. ) on the SerData line synchronously to SerClk (fig. ).The end of the word is signaled to Helix128-2 by activating SerLoad; note that SerClk must continue running at least one more cycle.A Helix128-2 serial data frame consists of the following components:. The broadcast or common set bit; if set, the chipaddress decoding is overridden and the register is set to the specified value. The chip address; the 6 bits of the chip address are compared tothe signals of the ID pads. If they do not match, the following bits are ignored (unless the broadcast bit has been set).

Serial Communication Protocol

The register address; the 5 bits specify the address of theregister to be written to. The data word; the 8 bits contain the value the specified register is setto.Data are written into the chip with the MSB first. Shows the map of the register addresses.